SPI verilog代码,已通过仿真与FPGA验证。可以集成在FPGA里面,迅速开发成品。 兄弟差积分,就顺手上传了一些项目资料。

”SPI verilog代码 已通过仿真与FPGA验证“ 的搜索结果

完成了SPI-MASTER的设计,并且编写了测试程序testbench,检测SPI-MASTER模块的工作时序,通过软件仿真,来验证其功能的正确性,最终本设计达到预期目标和SPI通信要求。最后,本文还将从功能、速度、面积、成本等方面...

基于verilog的SPI通信接口的代码

利用SPI实现FPGA和外设之间的通信。经过Modelsim仿真验证。(为FPGA设计技巧与案例开发详解一书源码)

FPGA学习之路——SPI详解及Verilog源码分析 概述 SPI = Serial Peripheral Interface,是串行外围设备接口,是一种高速,全双工,同步的通信总线。 优点 支持全双工 支持高速 协议支持字长不限于8bit,可以根据应用...

这次重新写了一遍初学FPGA时写的SPI主机驱动,减少了代码量,舍弃了状态机,补充了同时发送和接受功能的验证 代码 //Module Name:SPI Master //Author:Yang Cheng Yu //Date:2020/4/20 `define SIM module spi_...

这个资源的SPI_salver部分主要来源于博客,我自己修改了一部分。SPI_master部分是我自己写的,同时添加了testbench文件,在vivado平台上仿真通过,K7硬件上也验证成功。建议先看我的博客再下载。

大家好,最近试了很一些spi通信在verilog中的实现方案,最终写了一个比较简单的方案。分享给大家,代码需要可自取。

在Xilinx ISE 中对该模块进行综合与实现,并在FPGA 上完成了与验证。 引言 SPI(串行外围接口)总线,是一个同步串行接口的数据总线,它具有全双工、信号线少、协议简单、传输速度快等优点。由于串行总线的...

最后在Xilinx ISE 中对该模块进行综合与实现,并在FPGA 上完成了下载与验证。 引言 SPI(串行外围接口)总线,是一个同步串行接口的数据总线,它具有全双工、信号线少、协议简单、传输速度快等优点。由于串行...

文章目录一、SPI二、看spi--...重要的时间三、状态机设计1.i2c接口状态机2.flash读状态机3.flash写状态机四、代码部分1.==spi_interface.v==2.==spi_read_ctrl.v==3.==spi_write_ctrl.v==4.==spi_control.v==5.==top.

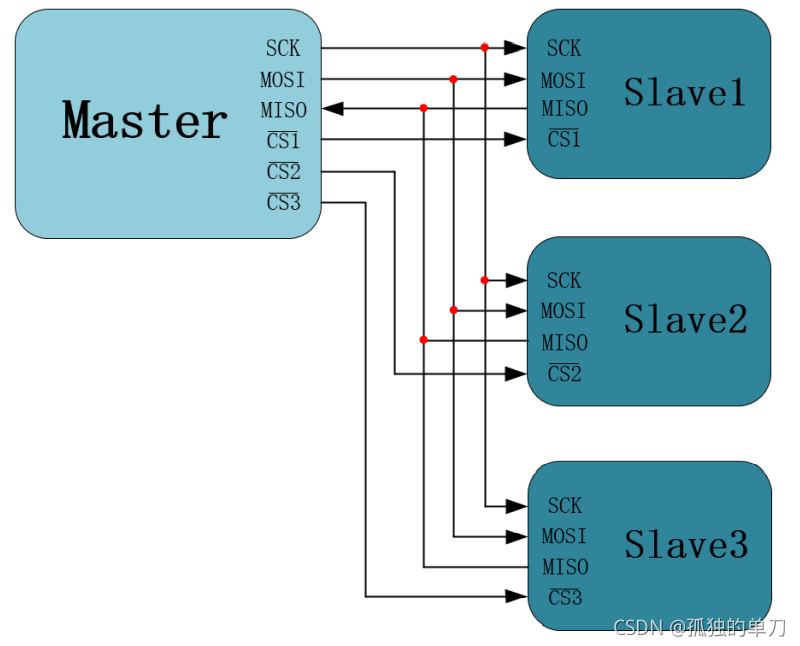

SPI通信模式为主-从模式 ,分为一主一从、一主多从:片选线CS用于主机选择对应的从机进行通信,片选线置低电平为通信开始信号,被拉高则为开始信号。

SPI功能模型,可以用于SPI的仿真验证工作,对其进行测试

你还可以通过仿真工具提供的调试功能来检查和验证SPI通信的正确性。 需要注意的是,FPGA仿真可能会涉及到一些复杂的设置和步骤,具体的操作方法可能会因为使用的FPGA开发板和仿真工具而有所不同。建议你查阅相关的...

综合仿真:Vivado 2018.3 芯片验证:Zynq7010 SPI模式 极性:CPOL 相位:CPHA Mode0 CPOL=0, CPHA=0 Mode1 CPOL=0, CPHA=1 Mode2 CPOL=1, CPHA=0 Mode3 CPOL=1, CPHA=1 时钟极性CPOL: SPI空闲时,时钟信号...

SPI总线控制代码,带有注释,仿真验证通过

★基础入门 1.FPGA开发软件安装

软件仿真、硬件仿真、原型验证这三种方法通过各自的优点和功能,共同为芯片设计提供了一种全面而高效的验证手段,有助于加速整个芯片开发周期,同时确保设计的正确性。在先进工艺的推动下,异构计算架构已逐渐成为...

同时,使用Verilog对FPGA进行编程可以实现系统级设计,并将电路设计、仿真和验证的时间缩短。 在使用ads1278进行数据采集时,需要在FPGA中使用SPI接口进行通信,并对接收到的数据进行处理,可以使用FPGA的高速处理...

通常情况下,这种代码可以通过一些特定的硬件设计语言(HDL)比如Verilog或者VHDL来实现。 在这个代码中,首先需要定义好SPI接口协议的通信方式,包括时钟、数据线、使能信号等。然后需要设计好FPGA内部的存储单元...

Verilog源代码,有注释,仿真通过,上板验证通过,工作时钟频率约为0.8M/s。不调用IP,纯逻辑实现,可用于各种FPGA和CPLD。

推荐文章

- 机器学习之超参数优化 - 网格优化方法(随机网格搜索)_网格搜索参数优化-程序员宅基地

- Lumina网络进入SDN市场-程序员宅基地

- python引用传递的区别_php传值引用的区别-程序员宅基地

- 《TCP/IP详解 卷2》 笔记: 简介_tcpip详解卷二有必要看吗-程序员宅基地

- 饺子播放器Jzvd使用过程中遇到的问题汇总-程序员宅基地

- python- flask current_app详解,与 current_app._get_current_object()的区别以及异步发送邮件实例-程序员宅基地

- 堪比ps的mac修图软件 Pixelmator Pro 2.0.6中文版 支持Silicon M1_pixelmator堆栈-程序员宅基地

- 「USACO2015」 最大流 - 树上差分_usaco 差分-程序员宅基地

- Leetcode #315: 计算右侧小于当前元素的个数_找元素右边比他小的数字-程序员宅基地

- HTTP图解读书笔记(第六章 HTTP首部)响应首部字段_web响应的首部内容-程序员宅基地